- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

실리콘 온 절연체 웨이퍼

VeTek Semiconductor는 Silicon On Insulator Wafer, ALD Planetary Base 및 TaC Coated Graphite Base를 전문적으로 생산하는 중국 제조업체입니다. VeTek Semiconductor의 Silicon On Insulator Wafer는 중요한 반도체 기판 재료이며 우수한 제품 특성으로 인해 고성능, 저전력, 고집적 및 RF 애플리케이션에서 핵심 역할을 합니다. 우리는 당신과의 추가 협력을 기대합니다.

문의 보내기

작동 원리VeTek 반도체'에스실리콘 온 절연체 웨이퍼주로 독특한 구조와 재료 특성에 의존합니다. 그리고 SOI 웨이퍼3개의 레이어로 구성됩니다. 상단 레이어는 단결정 실리콘 장치 레이어이고, 중간은 절연 BOX(Buried Oxide) 레이어이며, 하단 레이어는 지지 실리콘 기판입니다.

절연층의 형성: Silicon On Insulator Wafer는 일반적으로 Smart Cut™ 기술이나 SIMOX(Separation by IMplanted OXygen) 기술을 사용하여 제조됩니다. Smart Cut™ 기술은 실리콘 웨이퍼에 수소 이온을 주입해 버블층을 형성한 뒤, 수소가 주입된 웨이퍼를 지지하는 실리콘 웨이퍼에 접착시키는 기술이다. 열처리 후에 수소가 주입된 웨이퍼는 버블층에서 분리되어 SOI 구조를 형성합니다. SIMOX 기술은 고에너지 산소 이온을 실리콘 웨이퍼에 주입하여 고온에서 실리콘 산화물 층을 형성합니다.

기생 용량 감소: BOX 레이어의실리콘 온 절연체 웨이퍼장치 레이어와 베이스 실리콘을 효과적으로 분리하여 기생 커패시턴스를 크게 줄입니다. 이러한 격리는 전력 소비를 줄이고 장치 속도와 성능을 향상시킵니다.

래치업 효과 방지: n-well과 p-well 장치는 다음과 같습니다.SOI 웨이퍼완전히 분리되어 기존 CMOS 구조의 래치업 효과를 방지합니다. 이를 통해Silicon On Insulator 웨이퍼 더 빠른 속도로 제조됩니다.

에칭 정지 기능: SOI 웨이퍼의 단결정 실리콘 소자층과 BOX층 구조는 MEMS 및 광전자 소자 제조를 용이하게 하여 우수한 식각 정지 기능을 제공합니다.

이러한 특징을 통해,실리콘 온 절연체 웨이퍼반도체 공정에서 중요한 역할을 하며 집적 회로(IC) 및 미세 전자 기계 시스템(MEMS) 산업의 지속적인 발전을 촉진합니다. 우리는 진심으로 귀하와의 더 많은 소통과 협력을 기대합니다.

제품 매개변수:

생산 상점:

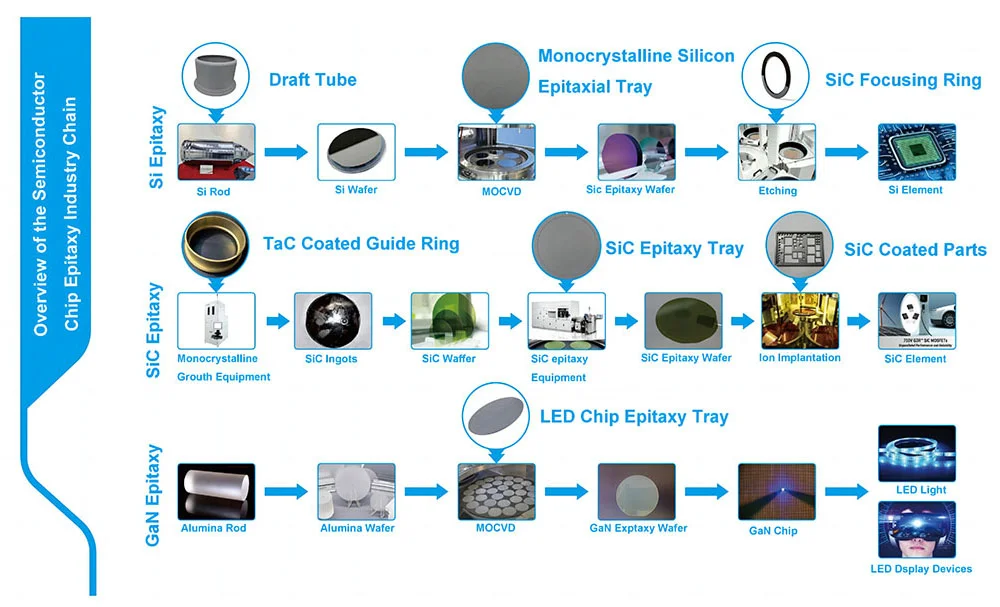

반도체 칩 에피택시 산업 체인 개요: