- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

칩 제조: MOSFET의 공정 흐름

2024-07-31

칩 제조 공정에는 포토리소그래피,에칭, 확산, 박막, 이온 주입, 화학 기계적 연마, 세척 등. 이 기사에서는 이러한 프로세스가 순차적으로 통합되어 MOSFET을 제조하는 방법을 대략적으로 설명합니다.

1. 우리는 먼저기판최대 99.9999999%의 실리콘 순도를 자랑합니다.

![]()

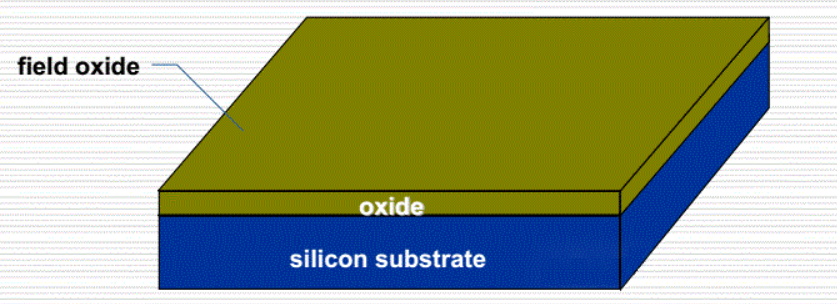

2. 실리콘 결정 기판에 산화막 층을 성장시킵니다.

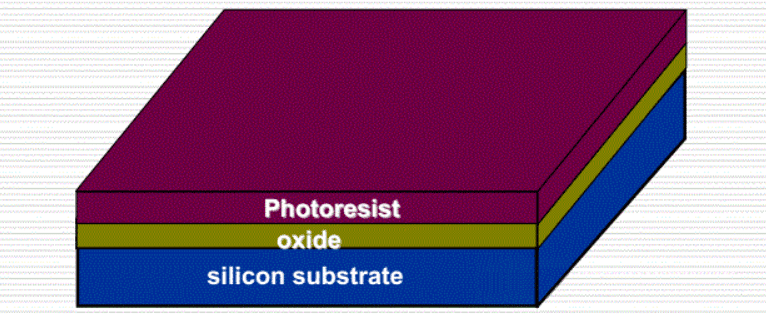

3. 포토레지스트를 고르게 스핀 코팅합니다.

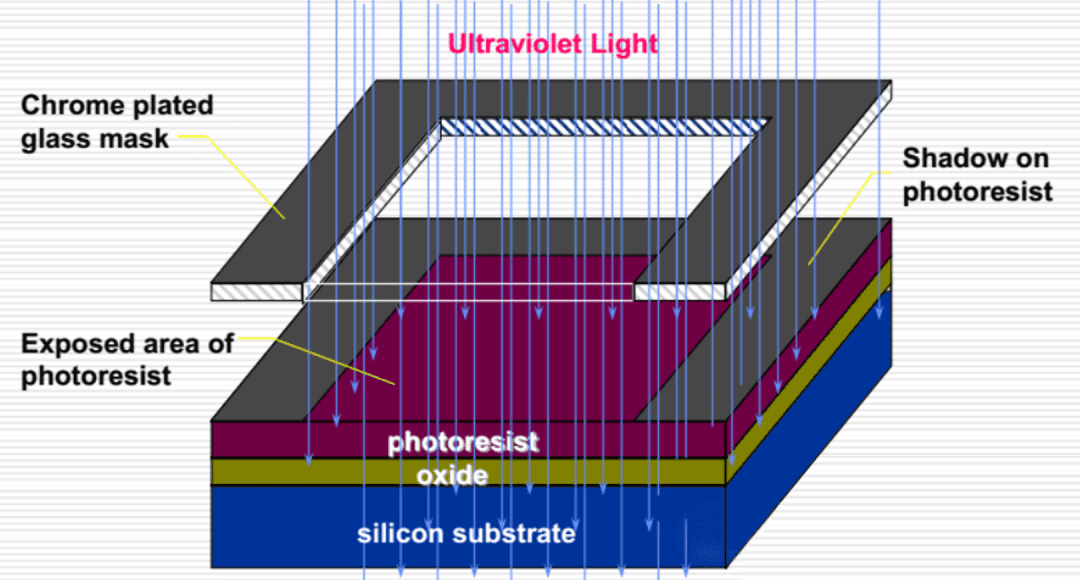

4. 포토마스크를 통해 포토리소그래피를 수행하여 포토마스크의 패턴을 포토레지스트에 전사합니다.

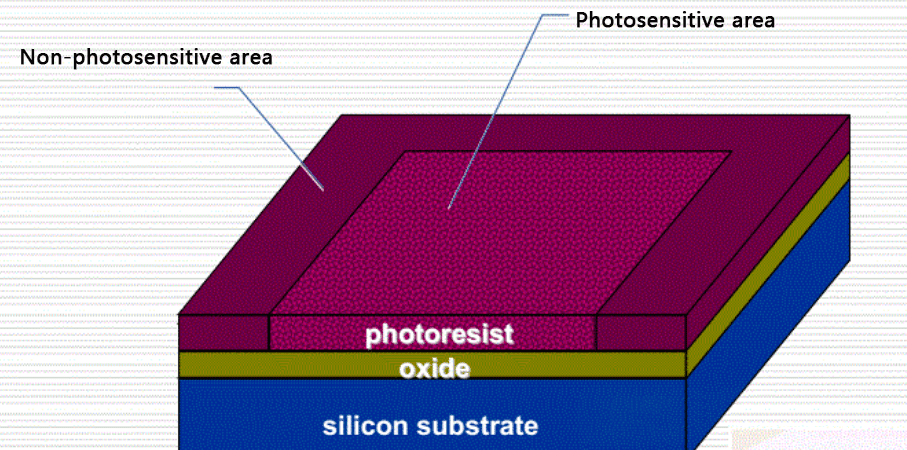

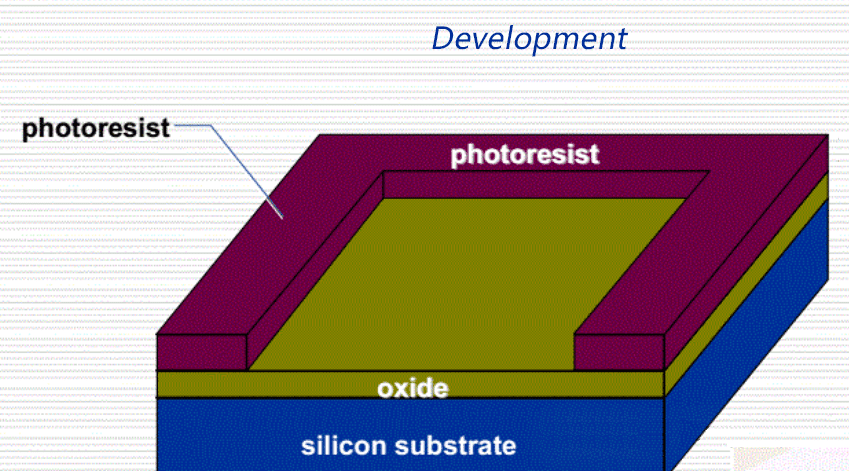

5. 감광성 영역의 포토레지스트는 현상 후 씻어냅니다.

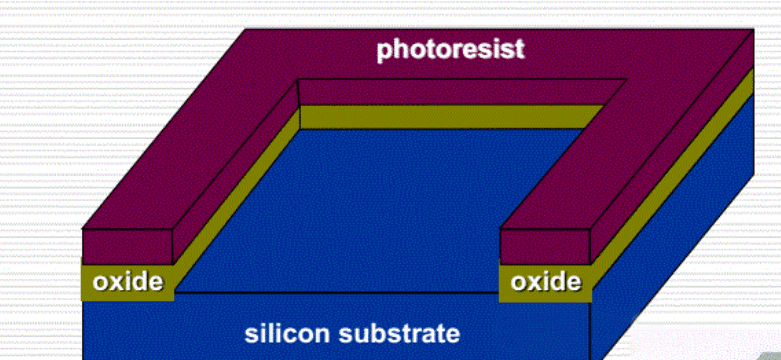

6. 포토레지스트로 덮이지 않은 산화막을 에칭을 통해 에칭하여 포토리소그래피 패턴이 전사되도록 합니다.웨이퍼.

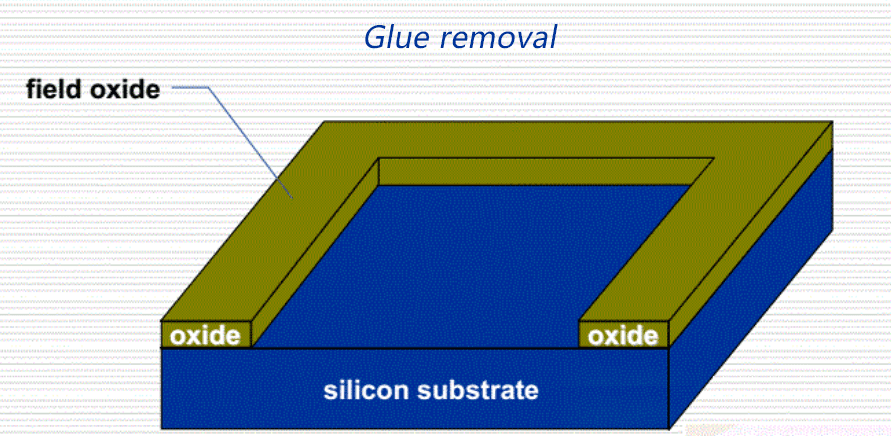

7. 남은 포토레지스트를 청소하고 제거합니다.

8. 다른 신너를 바르세요산화막. 그 후, 위와 같은 포토리소그래피와 에칭을 통해 게이트 영역의 산화막만 남게 된다.

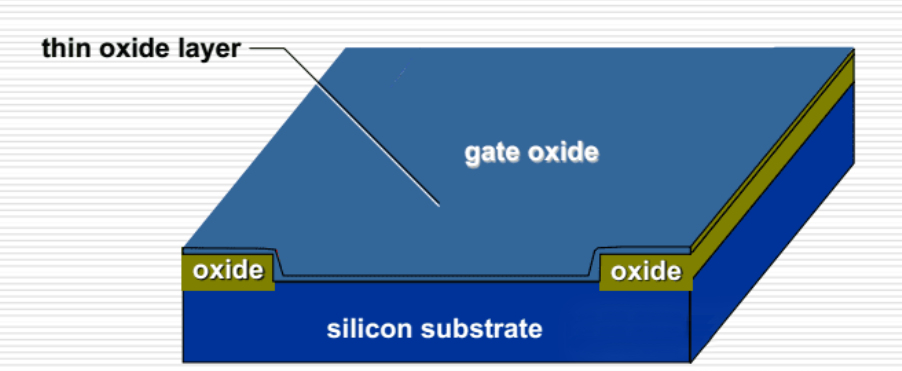

9. 그 위에 폴리실리콘 층을 성장시키세요

![]()

10. 7단계와 마찬가지로 포토리소그래피와 에칭을 이용해 게이트 산화막 위에 폴리실리콘만 남겨둔다.

![]()

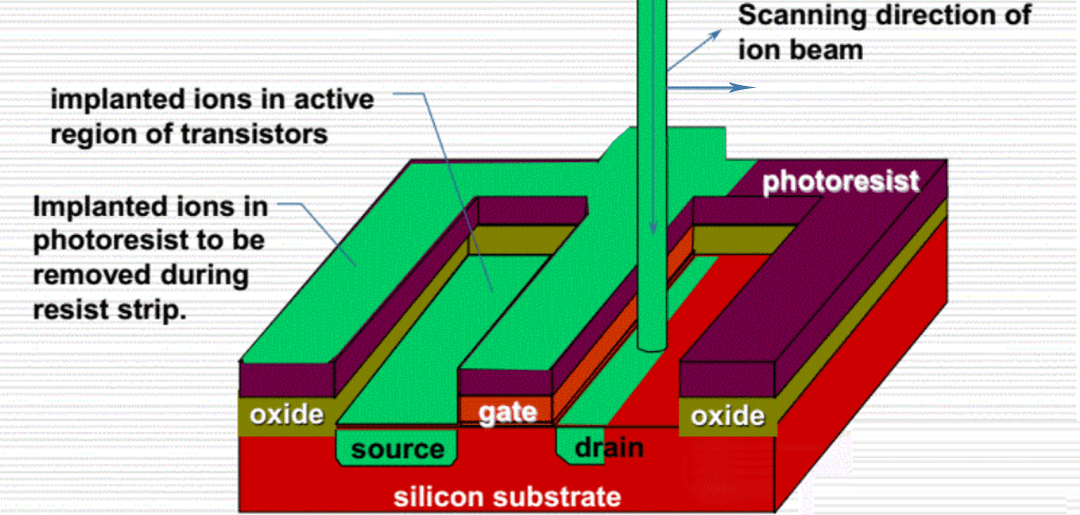

11. 포토리소그래피 세척으로 산화물 층과 게이트를 덮어 웨이퍼 전체가이온 주입, 소스와 드레인이 있습니다.

![]()

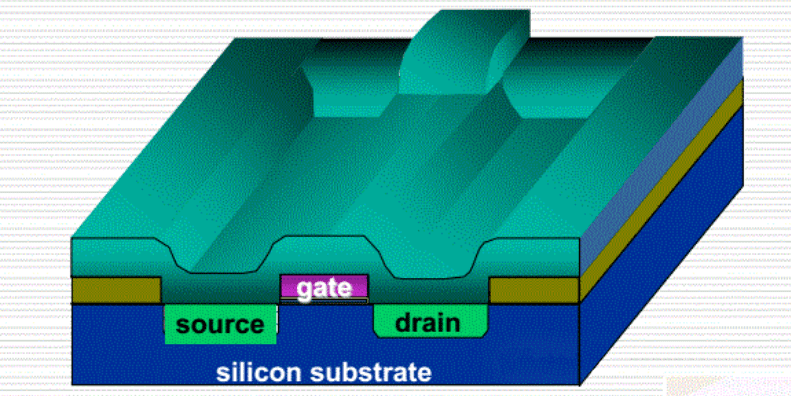

12. 웨이퍼 위에 절연막 층을 성장시킵니다.

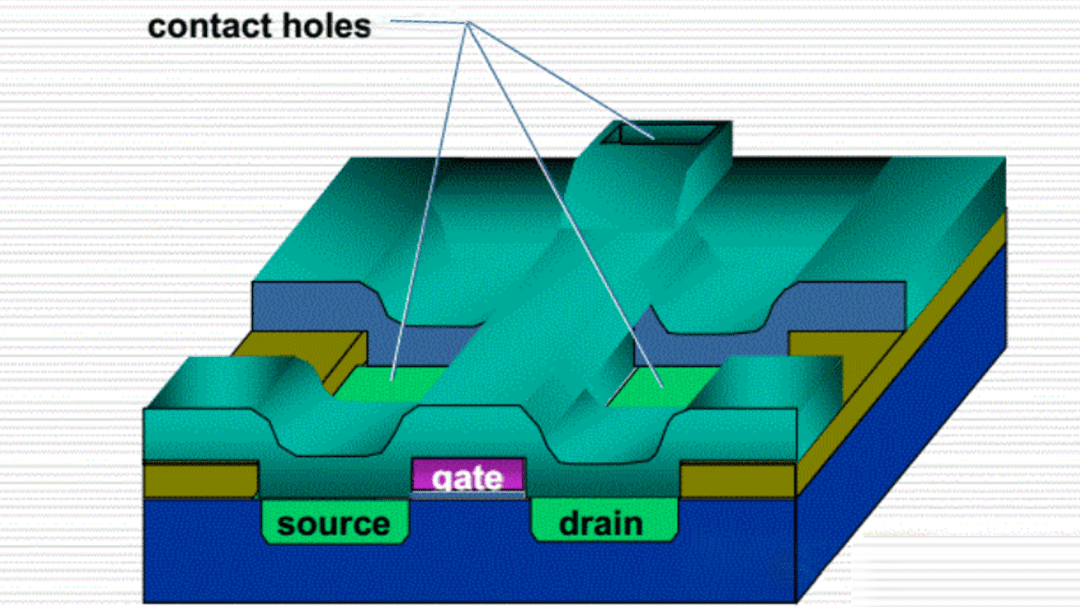

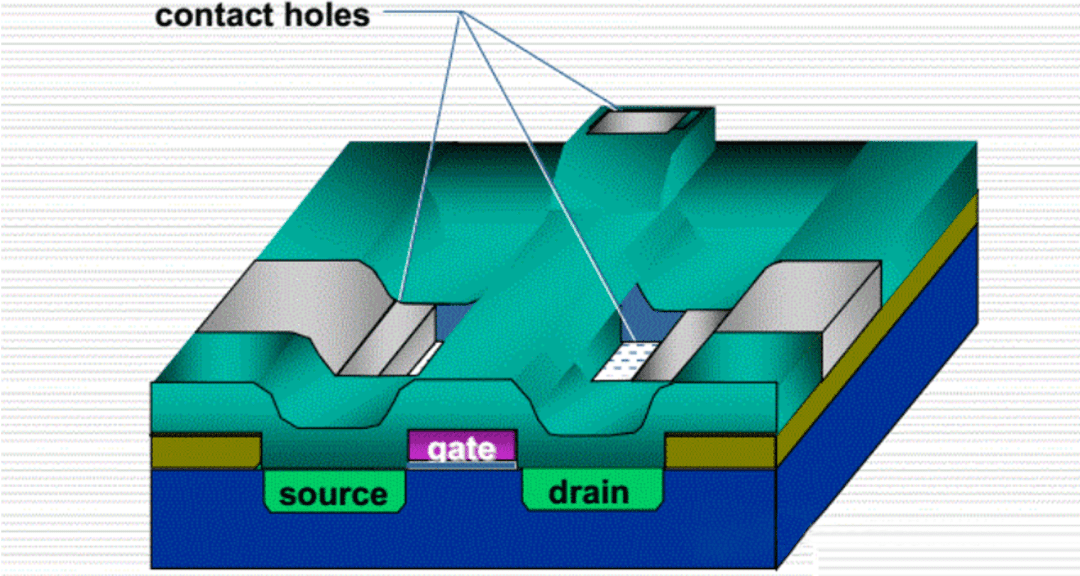

13. 포토리소그래피와 에칭을 통해 소스, 게이트, 드레인의 콘택홀을 에칭합니다.

14. 그런 다음 에칭된 영역에 금속을 증착하여 소스, 게이트 및 드레인용 전도성 금속 와이어가 있도록 합니다.

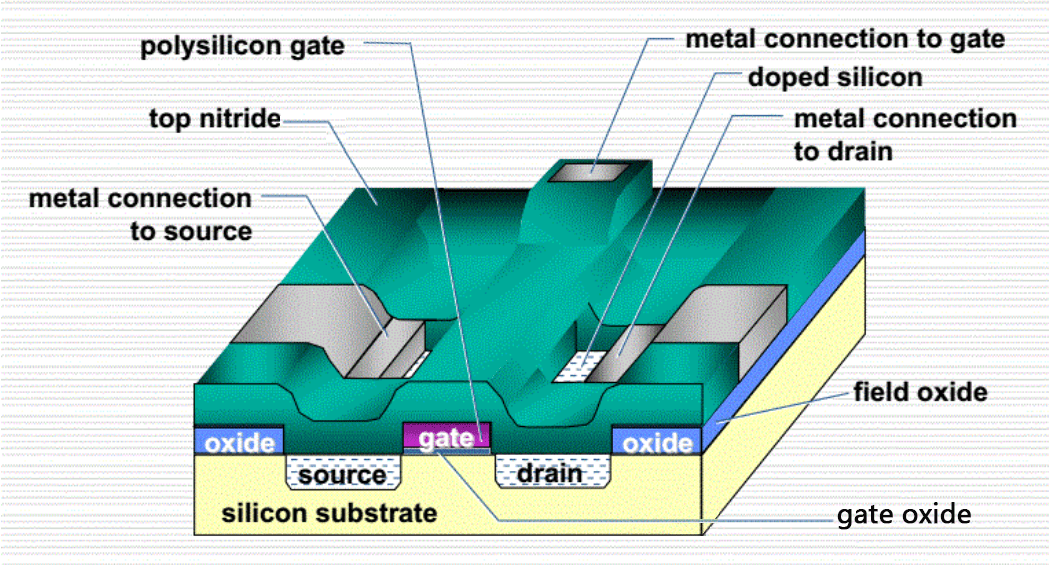

마지막으로 다양한 공정의 조합을 통해 완전한 MOSFET이 제조됩니다.

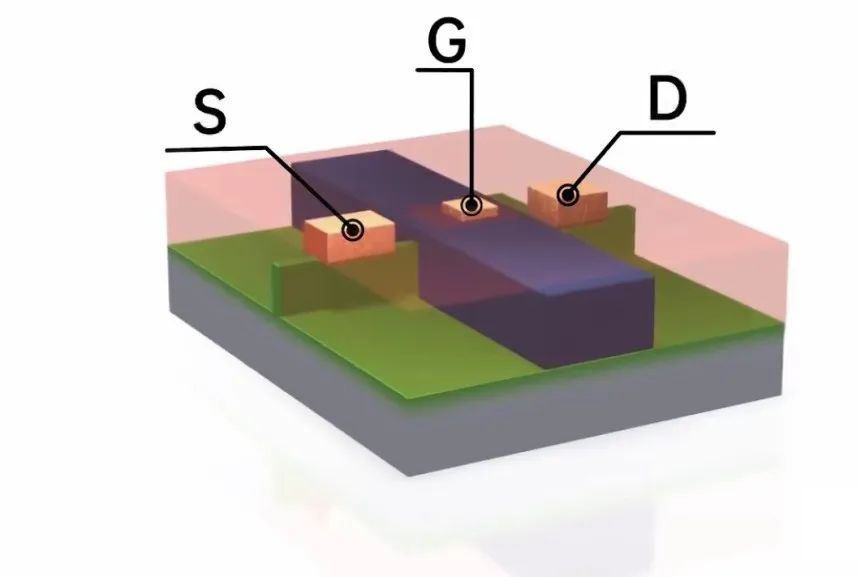

실제로 칩의 하단 레이어는 수많은 트랜지스터로 구성됩니다.

MOSFET 제조 다이어그램, 소스, 게이트, 드레인

![]()

다양한 트랜지스터가 논리 게이트를 형성함

![]()

논리 게이트는 산술 단위를 형성합니다.

![]()

마지막으로 손톱만한 크기의 칩입니다.

![]()