- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

칩 제조: 원자층 증착(ALD)

2024-08-16

반도체 제조 산업에서는 장치 크기가 계속 작아짐에 따라 박막 재료의 증착 기술이 전례 없는 어려움을 겪고 있습니다. 원자층증착(ALD)은 원자 수준에서 정밀한 제어가 가능한 박막 증착 기술로 반도체 제조에 없어서는 안 될 부분이 되었습니다. 이 글은 ALD의 공정 흐름과 원리를 소개하여 ALD의 중요한 역할을 이해하는 데 도움을 주기 위해 작성되었습니다.고급 칩 제조.

1. 자세한 설명ALD프로세스 흐름

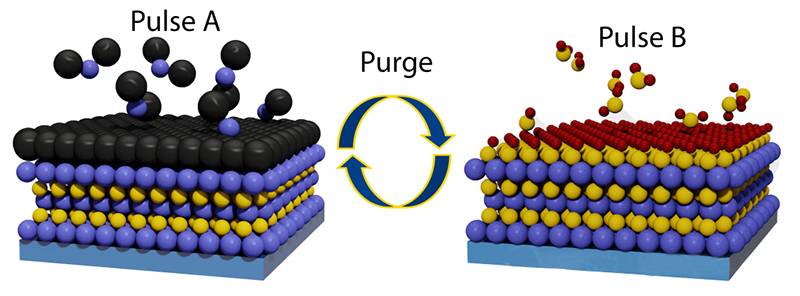

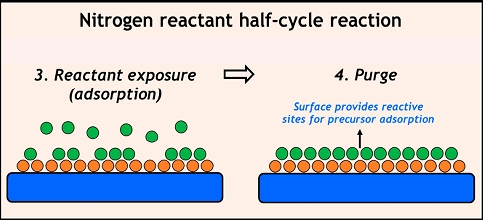

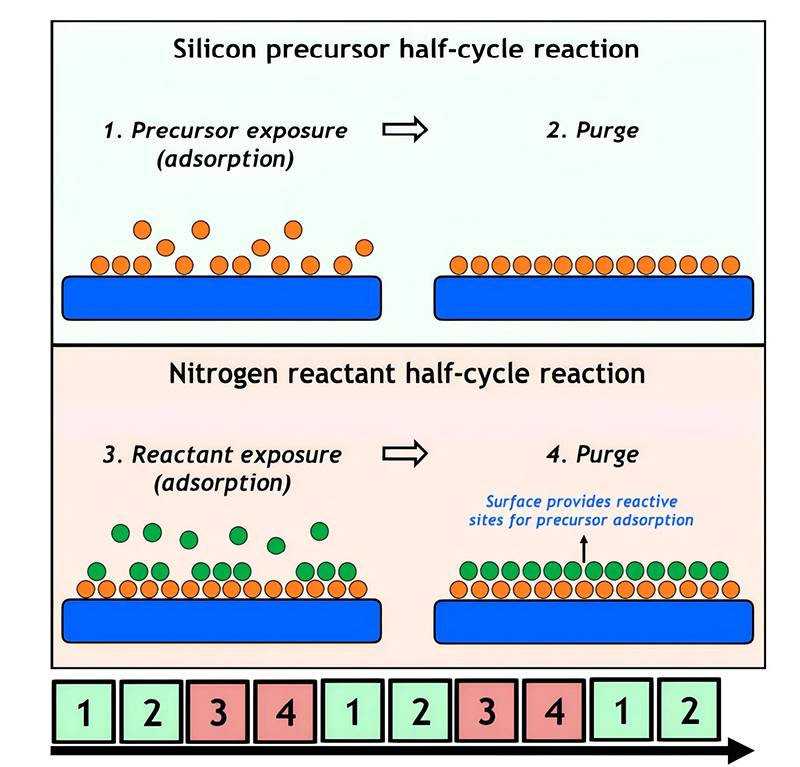

ALD 공정은 증착할 때마다 하나의 원자층만 추가되도록 엄격한 순서를 따르므로 막 두께를 정밀하게 제어할 수 있습니다. 기본 단계는 다음과 같습니다.

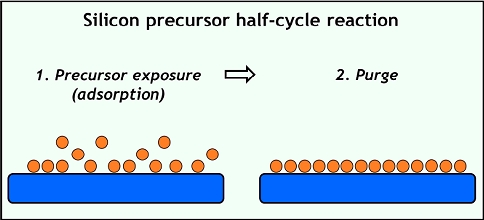

전구체 펄스:ALD공정은 첫 번째 전구체를 반응 챔버에 도입하는 것으로 시작됩니다. 이 전구체는 대상 증착 재료의 특정 활성 사이트와 반응할 수 있는 화학 원소를 포함하는 가스 또는 증기입니다.웨이퍼표면. 전구체 분자는 웨이퍼 표면에 흡착되어 포화된 분자층을 형성합니다.

불활성 가스 퍼지: 이어서, 반응하지 않은 전구체와 부산물을 제거하기 위해 퍼지를 위해 불활성 가스(예: 질소 또는 아르곤)를 도입하여 웨이퍼 표면이 깨끗하고 다음 반응을 위한 준비가 되도록 합니다.

두 번째 전구체 펄스: 퍼지가 완료된 후 두 번째 전구체가 도입되어 첫 번째 단계에서 흡착된 전구체와 화학적으로 반응하여 원하는 증착물을 생성합니다. 이 반응은 일반적으로 자체 제한적입니다. 즉, 모든 활성 부위가 첫 번째 전구체에 의해 점유되면 새로운 반응은 더 이상 발생하지 않습니다.

불활성가스 재퍼지 : 반응이 완료된 후 불활성가스를 다시 퍼지하여 잔류 반응물 및 부산물을 제거하고 표면을 깨끗한 상태로 복원하며 다음 사이클을 준비합니다.

이 일련의 단계는 완전한 ALD 사이클을 구성하며, 사이클이 완료될 때마다 원자층이 웨이퍼 표면에 추가됩니다. 사이클 수를 정밀하게 제어함으로써 원하는 필름 두께를 얻을 수 있습니다.

(ALD 1사이클 스텝)

2. 프로세스 원리 분석

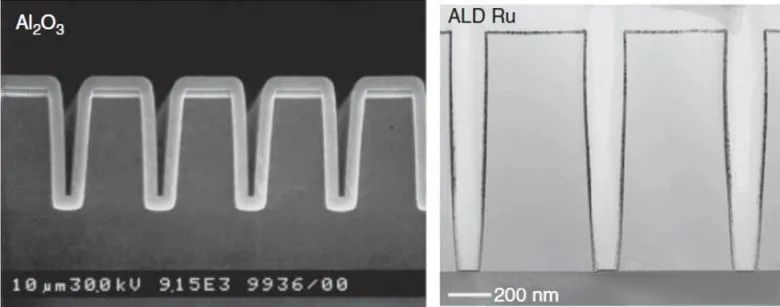

ALD의 자체 제한 반응은 핵심 원리입니다. 각 사이클에서 전구체 분자는 표면의 활성 부위와만 반응할 수 있습니다. 이러한 위치가 완전히 채워지면 후속 전구체 분자가 흡착될 수 없으므로 각 증착 라운드에 한 층의 원자 또는 분자만 추가됩니다. 이 기능으로 인해 ALD는 박막을 증착할 때 매우 높은 균일성과 정밀도를 갖게 됩니다. 아래 그림과 같이 복잡한 3차원 구조물에서도 좋은 스텝 커버리지를 유지할 수 있습니다.

3. 반도체 제조에 ALD 적용

ALD는 다음을 포함하되 이에 국한되지 않는 반도체 산업에서 널리 사용됩니다.

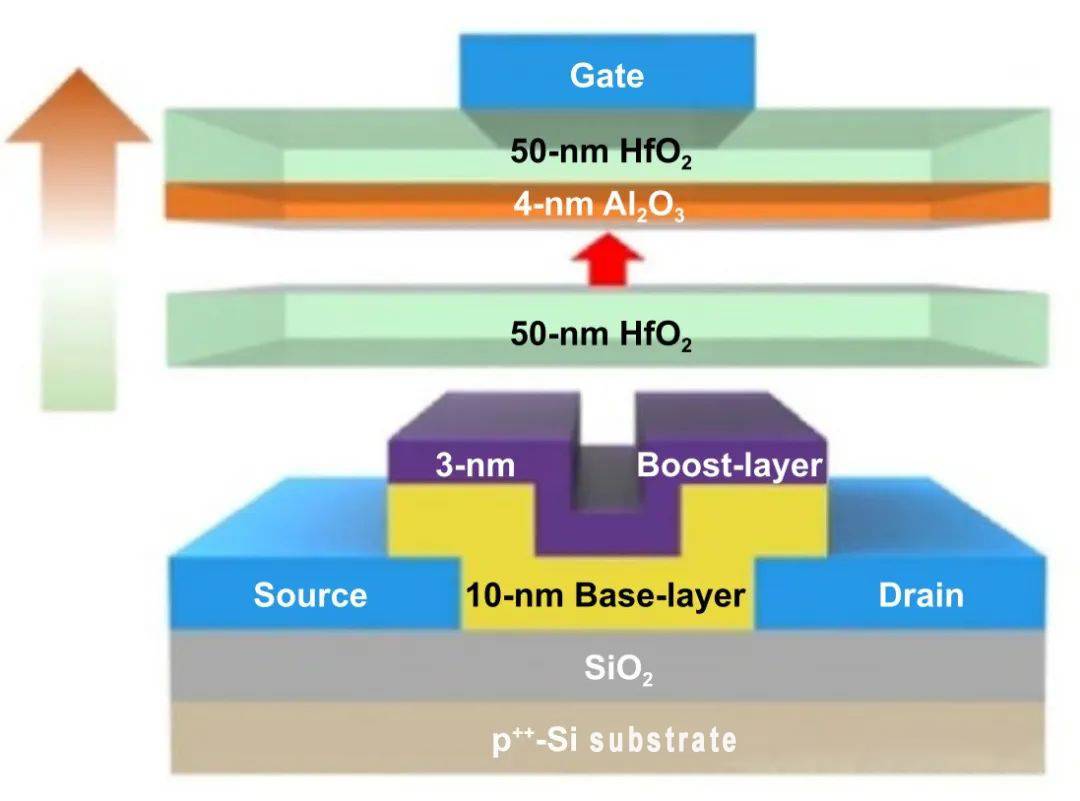

High-k 재료 증착: 차세대 트랜지스터의 게이트 절연층에 사용되어 장치 성능을 향상시킵니다.

금속 게이트 증착: 질화티타늄(TiN), 질화탄탈륨(TaN) 등 트랜지스터의 스위칭 속도와 효율을 향상시키는 데 사용됩니다.

상호 연결 장벽층: 금속 확산을 방지하고 회로 안정성과 신뢰성을 유지합니다.

3차원 구조 충진: 더 높은 통합을 달성하기 위해 FinFET 구조의 채널 충진과 같은 것입니다.

원자층 증착(ALD)은 뛰어난 정밀도와 균일성으로 반도체 제조 산업에 혁명적인 변화를 가져왔습니다. 엔지니어는 ALD의 프로세스와 원리를 숙지함으로써 나노 수준에서 뛰어난 성능을 갖춘 전자 장치를 구축할 수 있으며 정보 기술의 지속적인 발전을 촉진할 수 있습니다. 기술이 계속 발전함에 따라 ALD는 미래 반도체 분야에서 더욱 중요한 역할을 하게 될 것입니다.